# CUDA

Introduction **GPU Design Tenets Terminology Programming Basics** Access Pattern Workflow **Programming Model** Software View Hardware View **Full View and Restrictions** Efficiency/Optimization Libraries **CUDA Kernels** Example: CPU vs GPU **Dimensionality** Launching **Defining Threads and Blocks Thread Limits Identifying** Debugging **CUDA Memory** Shared Memory Specify as Launch Parameter **Specify in Kernel** Synchronization Barriers **Global Memory Memory Management Functions Synchronization Barriers Atomics CUDA** Optimization **Tiered Memory**

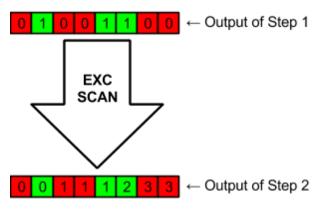

<u>Coalesced Global Memory Access</u> <u>Thread Occupancy</u> <u>Thread Divergence</u> <u>Thread Synchronization and Memory Access</u>

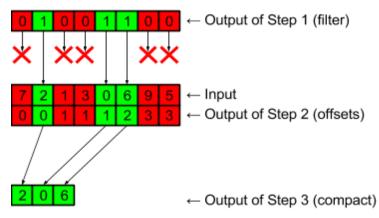

Fast Math Memory Copy (Host \sigma Device) Streams Algorithm Complexity Work Complexity vs Step Complexity Work Efficiency Algorithm Primitives Map **Special Cases** Gather Scatter **Stencil Transpose** Reduce **Implementations** Serial Parallel **Practical Considerations** Number of Parallel Units Floating Point Arithmetic / Non-associative Operators Scan Variations **Implementations** Serial Parallel (Naive) Parallel (Hillis-Steele) Parallel (Blelloch) **Practical Considerations** Number of Parallel Units and Algorithm Choice Floating Point Arithmetic / Non-associative Operators Segmented Scan Algorithm Patterns **Histogram** Serial Parallel (Atomic Add) Parallel (Thread Local Histogram and Atomic Add) Parallel (Thread Local Histogram and Reduce) Compact (Filter)

Serial Parallel **Allocation Serial** Parallel Sparse Matrix Vector Multiplication (SpMV) Serial Parallel Sorting Networks Serial Parallel Brick/Odd-Even Sort (Sorting Network) Serial Parallel **Bitonic Sort (Sorting Network)** Serial Parallel Merge Sort Serial Parallel Radix Sort **Serial** Parallel Algorithm Optimization **Data Layout Transformation** Tiling Privatization Partitioning (Binning)

# Introduction

Programming model specific to NVIDIA GPUs.

# **GPU** Design Tenets

Core GPU design tenets are as follows...

1. <u>Many simple compute units vs few powerful compute units</u> GPUs trade control for simpler computational units. For the programmer, that just means that you're more restricted in the way you write your programs.

#### 2. Explicitly parallel programming model

You have to model your software such it makes use of lots of execution threads. It isn't like programming for the CPU where you're more likely to write large chunks of code intended to run on a single thread.

Unlike programming for the CPU, the GPU is efficient at launching lots of threads and running them all in parallel. If you aren't running lots of threads, you aren't using the GPU effectively: "the GPU doesn't even get out of bed in the morning for fewer than 1000 threads."

#### 3. Optimized for throughput

GPUs are optimized to run many tasks at once, but not necessarily to run those tasks quickly.

### Terminology

- **<u>HOST</u>**  $\rightarrow$  PC that the GPU(s) are in.

- **<u>DEVICE</u>**  $\rightarrow$  GPU.

- **<u>KERNEL</u>**  $\rightarrow$  program to run on GPU (multiple copies of the same kernel run in parallel).

- <u>THREAD</u> → execution thread of our kernel (just like a CPU thread)

- **<u>BLOCK</u>**  $\rightarrow$  a block can run up to n threads of your kernel

- $\underline{SM} \rightarrow$  streaming multiprocessor (hardware component) that executes blocks

- **WARP CORE**  $\rightarrow$  SMs are made up of many warp cores (see thread divergence section)

- **<u>SIMD</u>**  $\rightarrow$  single instruction, multiple dataset (see thread divergence section)

- **<u>SIMT</u>**  $\rightarrow$  single instruction, multiple threads (see thread divergence section)

- **BARRIER** → thread synchronization pattern (wait for all threads to reach some point before continuing), see memory synchronization sections

- **ARRAY OF STRUCTS** (AOS)  $\rightarrow$  see transpose pattern section

- **<u>STRUCT OF ARRAYS</u>** (SOA)  $\rightarrow$  see transpose pattern section

- **<u>STEP COMPLEXITY</u>**  $\rightarrow$  see complexity section

- **WORK COMPLEXITY**  $\rightarrow$  see complexity section

- **WORK EFFICIENT**  $\rightarrow$  see complexity section

- <u>WEAK SCALING</u> → using parallelism to scale a problem so <u>larger/more</u> problems can be run at once

- **<u>STRONG SCALING</u>**  $\rightarrow$  using parallelism to scale a problem so it can be run <u>faster</u>

- <u>OCCUPANCY</u> → number of threads running per SM vs number of threads SM is capable of running

# **Programming Basics**

Access Pattern

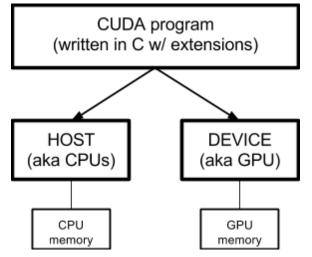

CUDA's programming model essentially looks like the following....

CUDA's tools allow you to write a single C program and target parts of your code to run on the GPU (called device) instead of your CPU (called host). You can write your program as a single whole C program, and the parts identified to run on the GPU (called kernels) will be compiled accordingly to run by the CUDA compiler.

Important things to note here...

- 1. <u>The host (CPU) is in charge</u> -- it runs the program and it gives directions to the device (GPU) on what to do: run task, copying to, copy from, etc...

- 2. <u>The host (CPUs) and the device (GPUs) have separate memory</u> -- there is no implicit way to view the memory between the two, you have explicitly shuttle data back and forth.

**NOTE**: Although multiple languages are supported, CUDA's main language is C.

**NOTE**: CUDA's "compiler" actually delegates complication of CPU-side C code to either GCC or MSVC. The only compiling that it actually does is the GPU portion?

#### Workflow

The typical workflow for a CUDA program is as follows...

- 1. Host (CPU) allocates storage on the device (GPU)

- 2. Host (CPU) copies input data to the device (GPU)

- 3. Host (CPU) launches kernel(s) on the device (GPU) to process that input data and produce output data

- 4. Host (CPU) copies the output data from the device (GPU)

Obviously, there's overhead to copying data back and forth. As such, your typical GPU program should have a high ratio of computation to communication -- you send your data, do a lot of work, then grab the resulting data.

# **Programming Model**

#### Software View

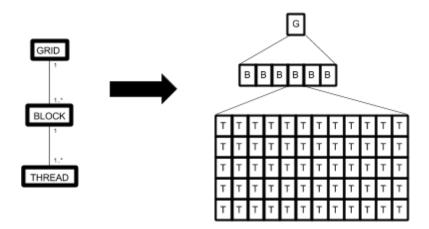

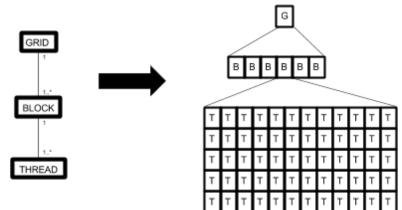

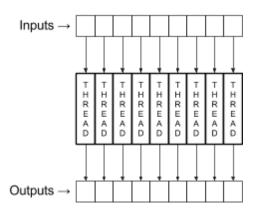

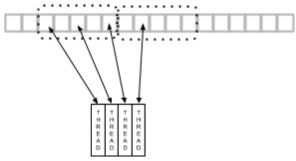

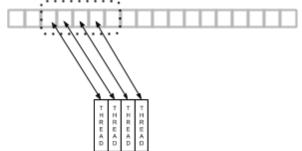

In software, you organize your execution <u>threads</u> to run as part of one or more <u>blocks</u>. Those blocks make up a <u>grid</u>.

#### Hardware View

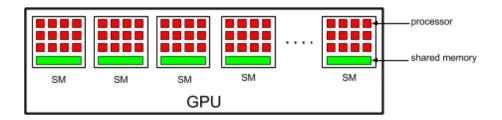

In hardware, the part of the NVIDIA GPU that executes your kernel is called an <u>SM</u> (streaming multiprocessor). There are multiple SMs in each GPU, and each of them is capable of running some fixed number of threads at once + it has some small amount of fixed memory that's local to it.

NOTE: For example, an NVIDIA 1080Ti has 28 SMs.

### Full View and Restrictions

Ultimately, a block maps entirely onto one SM. Since the threads within the block are all running on the same SM, those threads can cooperate with each other to potentially solve some sub-problem (remember that each SM has some shared memory).

You as the programmer don't have to worry about SMs. The underlying driver/hardware does the work of assigning blocks to SMs. Just be aware that you have no guarantees other than...

• your block will only ever run on 1 SM

(won't be split between SMs -- this is a driver/hardware level thing that we don't control)

only 1 kernel runs at once

(all blocks in a kernel finish before blocks on the next kernel run)

Other than that there are <u>NO GUARANTEES</u>, including...

- there's no way to get multiple kernels to run at once (all blocks in a kernel finish before blocks on the next kernel run)

- 2. there's no way to specify which SM runs which blocks (you can't assign a block to an SM)

- there's no way to specify when threads or blocks are run (you can't specify execution order of threads or blocks)

- 4. there's no guarantee that all your blocks will run at once (but there is a guarantee that all the threads in a single block will run at once)

- there's no way to split your blocks between multiple SMs (remember that blocks can only run on a single SM, and we can't access SMs directly)

- threads from different blocks cannot cooperate (only threads from the same block can communicate)

**NOTE**: These restrictions are what make the GPU fast. <u>Just remember that the only</u> <u>guarantee you have is that all the threads in a block will run together</u>.

# Efficiency/Optimization

To write efficient programs/kernels for GPUs, we need to maximize <u>arithmetic intensity</u>: amount of math operations we do vs the amount of time of time we spend fetching operands from memory for those math operations.

This boils down to...

- maximizing the math we do per thread (compute ops)

- minimizing the time spent on memory per thread (fetch/store ops)

We want to optimize for spending more time working and less time on accessing memory.

**NOTE**: Our focus here isn't necessarily to do LESS memory access, but to spend less TIME on memory access. There'll be more details on this in the memory section.

### Libraries

It can be very tedious and error prone to write your own implementations of low-level parallel algorithms in raw CUDA. Just like how you wouldn't want to write your own sorting algorithm every time you need to sort something, you don't want to write your own GPU parallel primitives every time you need to do something on the GPU.

There are a number of CUDA libraries that hide many of the little details when it comes to GPU programming...

- thrust → C++ STL for CUDA, it lets you do operations like scan, reduce, and a ton of other stuff via an STL-like library. It doesn't let you run kernels directly.

- cub → cub (CUda unBound) is a library that makes it easier to write CUDA kernels. It figures out low-level particulars of how your kernel should run (e.g. how much shared memory can it use, thread block size, etc..).

- $\bullet \quad \text{cublas} \to \text{blas library that uses CUDA}$

- $cuFFT \rightarrow fft$  library that uses CUDA

There are many more, but these seem to be the most popular.

# CUDA Kernels

The code your host (CPU) sends to your device (GPU) to run is called a kernel. <u>Kernels are</u> <u>coded as if they're serial programs -- they do not explicitly define anything related to parallelism</u>. The device (GPU) will launch multiple instances of the kernel to work on pieces of the data. Remember that a thread runs 1 copy of your kernel: threads are organized in blocks, and blocks are part of a grid.

# Example: CPU vs GPU

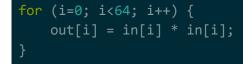

For example, imagine that you wanted to run some code to go over an array of floats and multiply power each by 2 (output = input<sup>2</sup>).

Here's how that would look if you were to write it serially for the CPU...

Here's how that would look if you were to write it for CUDA...

```

//

// Device-side (GPU) code. This is the kernel.

// __global__ declspec lets the compiler know that this is for the GPU

//

__global__ void square(float *d_out, float *d_in) {

int idx = threadIdx.x;

float f = d_in[idx];

d_out[idx] = f * f;

}

//

// Host-side (CPU) code. This launches the kernel.

//

void launchKernel() {

// allocate data on host (CPU)

float h_in[64] = { /* initial values */ }

float h_out[64];

// 1. allocate data on device (GPU)

float * d_in;

float * d_out;

cudaMalloc((void **) &d_in, 64*sizeof(float))

cudaMalloc((void **) &d_out, 64*sizeof(float))

```

```

// 2. copy inputs from host (CPU) to device (GPU)

cudaMemcpy(d_in, h_in, 64*sizeof(float), cudaMemcpyHostToDevice);

// 3. LAUNCH 1 BLOCK OF 64 THREADS + WAIT FOR THEM TO FINISH

square<<<1, 64>>>(d_out, d_in);

// 4. copy outputs from device (GPU) to host (CPU)

cudaMemcpy(h_out, d_out, 64*sizeof(float), cudaMemcpyDeviceToHost);

// 5. free data on device (GPU)

cudaFree(d_in);

cudaFree(d_out);

}

```

Notice that vars that...

- point to memory on the device (GPU) are prefixed with d\_

- point to memory on the host (CPU) are prefixed with h\_

This is an important visual identifier. You can't access memory on the device (GPU) from the host (CPU) or vice versa.

Notice what's happening host-side (CPU)...

- 1. it allocates memory on the device

- 2. copies input data to the device

- 3. runs the kernel (1 block of 64 threads)

- 4. copies output data from the device

- 5. frees the memory that was allocated on the device

Notice what's happening for device-side (GPU)...

- 1. code is written as if it's single threaded and intended to work on a single element

- 2. \_\_global\_\_ declspec is used to tell the compiler that this is device code

- 3. threadIdx is a global var that specifies which thread the copy of the kernel is on

- 4. the params match the args passed in

There's some extra overhead here (in terms of code we have to write) when compared to the single-threaded CPU equivalent. There isn't much that we can do about this.

# Dimensionality

It turns out that a lot of what CUDA is used for is image processing (2D) and real-world simulations (3D). As such, you can specify your blocks and/or threads as 1D, 2D, or 3D. In the graphic below, our threads are defined as a 2D block of 12x5 and our grid is a 1D block of 6...

The importance of this will be explained in further sections.

# Launching

If you looked at the example, you saw that we launched 1 block of 64 threads. The syntax for launching a kernel is...

```

func<<<NUM_BLOCKS, NUM_THREADS_PER_BLOCK, SHAREDMEM_PER_BLOCK>>>(...);

```

This is exactly like calling a function, except that you specify your launch parameters between the <<< and >>>.

Here's an example...

```

square<<<1, 64>>>(d_out, d_in);

```

**NOTE**: SHAREDMEM\_PER\_BLOCK wasn't specified in the example. It defaults to 0 if left out. This parameter will be discussed further in the memory section of the document.

Kernels launch asynchronously. That means that it won't block until the kernel finishes executing -- control will very likely be returned to you before the kernel finishes. If you want to block until the kernel finishes, you can call cudaDeviceSynchronize().

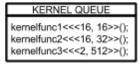

Remember that only 1 kernel can execute at once. If you launch multiple kernels back-to-back, they'll be put into a queue.

**NOTE**: Typically, kernels are launched from the host. But, newer versions of CUDA will allow you to launch a kernel from inside a kernel, where that parent kernel waits for the child kernels to finish. Look up dynamic parallelism.

#### **Defining Threads and Blocks**

It turns out that a lot of what CUDA is used for is image processing (2D) and real-world simulations (3D). As such, it has native support for specifying things in 2D and 3D.

If you looked at the threading example, you saw that there was a threadIdx global var that we used to determine which item to work on. We used the x member of that var, but that var is a struct with 3 members: x, y, and z.

When we launch our kernel, we can actually pass in dim3 structures for the NUM\_OF\_BLOCKS and NUM\_OF\_THREADS inputs. For example...

func<<<dim3(2, 2, 1), dim3(128, 128, 1)>>>(arg1, arg2, ...);

Then, in our kernel, we can go ahead and make use of the y and z members of threadIdx.

**NOTE**: There are other important global variables that need to be used to determine which part of the data you're suppose to work on. See the Identifying Threads section.

If we use ints instead of dim3s, it's effectively the same as specifying 1 for the y and z parameters...

```

// The following 2 lines are equivalent

func<<<1, 64>>>(arg1, arg2, ...);

func<<<dim3(1, 1, 1), dim3(64, 1, 1)>>>(arg1, arg2, ...);

```

#### Thread Limits

A device (GPU) can run many blocks at once, but there's a maximum number of threads per block. For older GPUs, this is 512. For newer GPUs, this is 1024 (possibly more? The lessons this is coming from are old).

Pick the combination of blocks and threads-per-block that makes the most sense for you. For example, if you wanted to run 1280 threads, you can try doing func<<<10,128>> (10 blocks of 128 threads-per-block). What you can't do is func<<<1,1280>> -- this is too many threads-per-block.

**NOTE**: Does the threads-per-block value have to be a power of 2? Tests show that it doesn't. But, it looks like in the example codes provided, the total size of the array

passed into the kernel as an arg, and a guard is in place in the kernel to make sure it doesn't process out of bounds items. It may be that this is needed in certain cases.

# Identifying

Remember that multiple copies of your kernel run at once (each in its own threads). There are global variables that you can access in your kernel code to help identify which thread it's running in.

In the squaring example, we used the global var threadIdx to determine which part of the data we need to work on. This is all we needed because we used a block size of 1. If we used more than 1 block, we would need to make use of other global vars as well to work out which part of the data we need to work on...

- threadIdx  $\rightarrow$  which <u>thread</u> we're running on (relative to the block we're running on)

- blockIdx  $\rightarrow$  which <u>block</u> we're running on

- blockDim → number of threads specified for each block

- gridDim  $\rightarrow$  number of <u>blocks specified</u>

For example, if our kernel only deals with 1 item per thread (and we're only dealing with 1D data), we can find out which item we should be working on using this simple formula...

unsigned int idx = blockIdx.x \* blockDim.x + threadIdx.x

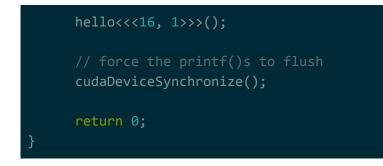

# Debugging

You can debug your CUDA kernels by calling <u>printf()</u> directly in the kernel. Once your kernel launch finishes, you need to call <u>cudaDeviceSynchronize()</u> to flush the stuff you printed out.

Obviously, there's overhead here. You should avoid calling printf() unless absolutely required.

Here's an example...

```

#include <stdio.h>

#include <stdib.h>

___global__ void hello() {

printf("I'm a thread %d of block %d\n", threadIdx.x, blockIdx.x);

}

int main(void) {

// launch kernels

```

This is what the output looks like...

I'm a thread 0 of block 9 I'm a thread 0 of block 8 I'm a thread 0 of block 13 I'm a thread 0 of block 5 I'm a thread 0 of block 10 I'm a thread 0 of block 2 I'm a thread 0 of block 4 I'm a thread 0 of block 6 I'm a thread 0 of block 12 I'm a thread 0 of block 14 I'm a thread 0 of block 11 I'm a thread 0 of block 1 I'm a thread 0 of block 3 I'm a thread 0 of block 0 I'm a thread 0 of block 15 I'm a thread 0 of block 7

**NOTE**: If you're accessing shared memory from the printf call, you will need to call \_\_\_\_\_\_syncthreads() before you do, because the writes HAVE TO COMPLETE before you can call printf()!!!! THIS IS SUPER IMPORTANT. Don't know what \_\_\_\_\_syncthreads() is? Check the barrier section.

# **CUDA Memory**

The device (GPU) provide 3 levels of memory: local, shared, and global.

A thread has access to <u>local memory</u> (this is memory that's local to the thread -- e.g. stack memory?)

• Threads in the same block have access to shared memory (this is memory that can be accessed by any thread in the block)

• All threads, regardless of the block, have access to global memory (this is memory that can be accessed by any thread)

Essentially all this means is that...

- 1. threads from the same block can work together via shared memory

- 2. threads from different blocks can work together via global memory

The problem here is that there are multiple threads running at once, so if you're going to be reading and writing to the same location from different threads, you're going to run into thread/memory synchronization issues. Working around these will be discussed in a further section.

Obviously, local memory would be the fastest to access, followed by shared memory, followed by global memory.

# Shared Memory

You can specify some amount of memory to be shared by the threads in each block. Each thread in a block will have access that shared memory.

The 2 important things to note about shared memory...

- All blocks have the same amount of shared memory

- You cannot dynamically allocate shared memory in the kernel

There are 2 ways to specify shared memory...

• As a launch parameter  $\rightarrow$  use this if you need to define the amount of mem at runtime

• As an array in the kernel  $\rightarrow$  use this if you know the amount of mem at compile time

**NOTE**: Why use shared block memory? Apparently it's memory that's directly on the chip and as such is up to 100x faster to access than global GPU memory. There's also some nuance here when it comes to memory synchronization and stuff. I'll try to cover this in some other topic but for now just see this... https://devblogs.nvidia.com/parallelforall/using-shared-memory-cuda-cc/

**NOTE**: Apparently using shared memory takes away from the L1 cache on the device (GPU). Also the amount of shared memory you can have seems to be super small (16 to 64kb?).

Specify as Launch Parameter

You can specify the amount of memory via the the 3rd launch parameter (SHAREDMEM\_PER\_BLOCK)...

func<<<NUM\_BLOCKS, NUM\_THREADS\_PER\_BLOCK, SHAREDMEM\_PER\_BLOCK>>>(...);

For example, if I wanted to have 16 floats of shared memory in each block...

func<<<2, 64, sizeof(float)\*16>>>(arg1, arg2);

**NOTE**: The value passed in doesn't have to be a literal. You can compute some value and pass that in.

Once I want to access this in my kernel, I'd go to my kernel and stick in an extern'd unsized float array with a declspec of \_\_\_\_\_shared\_\_\_\_.

extern \_\_\_shared\_\_\_float s[];

#### Specify in Kernel

If you know the amount of memory you want to share at compile time, you can declare the array right inside the kernel instead of using a launch parameter. All you have to do is make sure you using a literal when declaring your array and have a declapec of \_\_\_\_\_shared\_\_\_ on it...

\_shared\_\_\_ int s[64];

#### Synchronization Barriers

You can synchronize your threads via a <u>barrier</u>. A barrier just means that all your threads will PAUSE execution at a certain point and wait for the others to finish...

To add a barrier in your kernel, you need to call \_\_\_\_synchthreads(). Below is a trivial example of using \_\_\_syncthreads() to shift the elements in an array left by one...

```

_global__ void shift_left(int * d_arr) {

int i = threadIdx.x;

__shared__ int shared[SIZE];

shared[i] = d_arr[i];

____syncthreads();

int temp = i == SIZE - 1 ? shared[i] : shared[i + 1];

____syncthreads();

shared[i] = temp;

____syncthreads();

d_arr[i] = shared[i];

int main(void)

shift_left<<<1, SIZE>>>(d_arr);

```

# The important thing with the above example is that 1 thread is assigned/isolated to 1 element in the array. So each thread...

- 1. copies the element it's responsible from global mem to shared mem

- 2. waits for other threads to catch up (all elements should be in shared mem at this point)

- 3. reads in the neighbouring element from shared mem

- 4. waits for other threads to catch up (all elements should be read at this point)

- 5. writes the neighbour to the element it's responsible for

- 6. waits for other threads to catch up (all elements should be written at this point)

- 7. copies the element it's responsible for back from shared mem to global mem

**NOTE**: This was just a trivial example to illustrate barriers.

NOTE: Calling printf on shared memory? You need a barrier before the printf.

# **Global Memory**

Global memory is memory that's shared between all threads on the device (GPU). Any thread can access it at any time. Just like how you can allocate/free memory on the host (CPU), you can allocate/free global memory on the device (GPU).

The thing to be aware of is that <u>you cannot allocate global memory directly from the kernel</u>. The allocating/freeing of global memory on the device (GPU) must happen on the host (CPU).

#### **Memory Management Functions**

The memory management functions for the device (GPU) are very similar to the host (CPU)...

- $\bullet \quad malloc \to cudaMalloc$

- memcpy  $\rightarrow$  cudaMemcpy

- memset  $\rightarrow$  cudaMemset

- free  $\rightarrow$  cudaFree

Remember that you <u>must allocate device global memory on the host</u>. You cannot allocate memory directly in the kernel thread. This means that cudaMalloc, cudaMemcpy, etc.. can only ever be called from the host.

For memory that sits on the host, the convention is to name the variable with a h\_ prefix. For memory that sits on the device, the convention is to name the variable with d\_ prefix.

#### }

#### **NOTE**: For the full list of memory management functions, see

http://docs.nvidia.com/cuda/cuda-runtime-api/group\_\_CUDART\_\_MEMORY.html#axzz4r HUZY4cw

```

Here's an example of the memory management functions being used...

```

```

// THIS IS ALL HAPPENING ON THE HOST

// YOU CANNOT ALLOCATE/FREE GLOBAL MEMORY IN KERNEL, ONLY IN HOST

// allocate data on host (CPU)

float h_in[64] = { /* initial values */ }

float h_out[64];

// 1. allocate data on device (GPU)

float * d_in;

float * d_out;

cudaMalloc((void **) &d_in, 64*sizeof(float))

cudaMalloc((void **) &d_out, 64*sizeof(float))

// 2. copy inputs from host (CPU) to device (GPU)

cudaMemcpy(d_in, h_in, 64*sizeof(float), cudaMemcpyHostToDevice);

// 3. LAUNCH KERNEL

square<<<1, 64>>>(d_out, d_in);

// 4. copy outputs from device (GPU) to host (CPU)

cudaMemcpy(h_out, d_out, 64*sizeof(float), cudaMemcpyDeviceToHost);

// 5. free data on device (GPU)

cudaFree(d_in);

cudaFree(d_out);

```

Note what's going on in the example...

- global device memory is being allocated on the host

- global device memory is being free'd on the host

- pointers to the allocated global device memory are being passed in as args to the kernel

- memory is being copied from host to device (can't device memory directly from host)

- memory is being copied from device to host (can't host memory directly from device)

- memory on host is prefixed with h\_ (this is just a style convention)

- memory on device is prefixed with d\_ (this is just a style convention)

#### Synchronization Barriers

There's no way to synchronize access to global memory like you do with shared memory.

The problem is that <u>your only guarantee is that threads within the same block will be</u> <u>started/running</u>. As such, those are the only threads you can synchronize via barriers.

If you have multiple blocks that have threads reading/writing to the same location in global memory, there's no guarantee that those blocks will all run at the same time. Some blocks may have to finish before others can run (we have no control over which blocks run or how many run at once).

We do have access to some synchronization functionality for global memory via atomics (explained in the next section).

#### Atomics

Atomics (short for atomic memory operations) are special instructions that the device implements for the purpose of fetching/storing memory atomically. Some examples include...

- Arithmetic ops  $\rightarrow$  atomicAdd, atomicSub, atomicInc, atomicDec

- Min/max ops  $\rightarrow$  atomicMin, atomicMax

- Bitwise ops  $\rightarrow$  atomicAnd, atomicOr, atomicXor

- Swap ops  $\rightarrow$  atomicCAS, atomicExch

**NOTE**: Many of these atomic functions are for integers types only. Apparently one of the issues is that <u>there's no ordering constraints</u> when these atomic operations are being applied. As such, you can't get accurate computations for floats.

The math property of <u>associativity doesn't apply for floating point numbers</u>... for example (a+b)+c != a+(b+c) - plug into any c compiler where a=1,  $b=10^{10}$ ,  $c=-10^{10}$ . If atomics were available for floats, you'd get different results for each run depending on the order in which your data was computed.

If you need to implement an atomic operation that isn't available (or for a type that isn't available), you can do so with atomicCAS, but it will be really awful. For example, here's atomicAdd written using atomicCAS...

```

__device__ int atomicAdd(int* address, int val) {

int old = *address, assumed;

do {

assumed = old;

old = atomicCAS(address, assumed, val + assumed);

} while (assumed != old);

```

return old;

These operations are implemented directly on the hardware. There is no special magic happening under the hood -- the hardware is pausing threads and shifting things around so that these atomic operations can happen.

It's not recommended you use atomics unless you really need to. They've been known to kill performance if you aren't careful.

For more information, see

http://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html#atomic-functions

**NOTE**: Having trouble thinking about this? Think of AtomicInteger in Java. It stops one thread from clobbering the results of another and provides access to basic instructions like add-and-get, get-and-add, etc...

NOTE: Here's an important note from the docs that may be handy in the future...

On GPU architectures with compute capability lower than 6.x, atomics operations done from the GPU are atomic only with respect to that GPU. If the GPU attempts an atomic operation to a peer GPU's memory, the operation appears as a regular read followed by a write to the peer GPU, and the two operations are not done as one single atomic operation. Similarly, atomic operations from the GPU to CPU memory will not be atomic with respect to CPU initiated atomic operations.

Compute capability 6.x introduces new type of atomics which allows developers to widen or narrow the scope of an atomic operation. For example, atomicAdd\_system guarantees that the instruction is atomic with respect to other CPUs and GPUs in the system. atomicAdd\_block implies that the instruction is atomic only with respect atomics from other threads in the same thread block.

NOTE: Atomics are for NVIDIA GPUs only?

# **CUDA** Optimization

The following subsections detail optimization patterns specific to the CUDA architecture.

# **Tiered Memory**

Remember how memory is broken up into a hierarchy: local, shared, and global. The way this is usually broken down...

- Local  $\rightarrow$  arguments and stack variables, sits on registers or L1 cache

- Shared  $\rightarrow$  shared between threads on a block, sits on SM that block is assigned to

- Global  $\rightarrow$  shared between all threads, sits on GPU card itself

The general rule is, as far as speed goes: <u>Local > Shared > Global</u>... Local will be faster than shared, and shared will be faster than global. As such, <u>you should move/cache more</u> <u>frequently-accessed data to faster memory</u>.

**NOTE**: This is general rule... but memory access can actually be a bit more nuanced.

**NOTE**: Shared memory is like a CPU's cache block, except that you have explicit control of it.

**NOTE**: Even though global memory is the slowest of the 3, it's still much faster than host (CPU) memory.

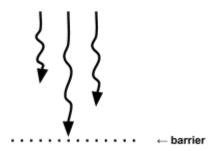

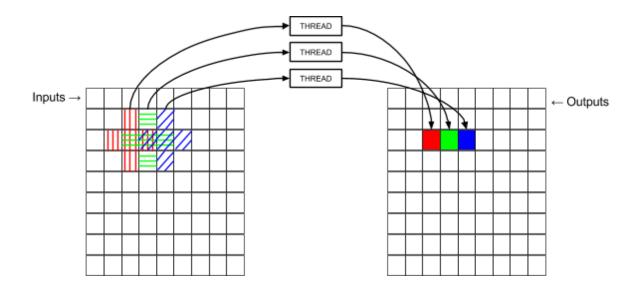

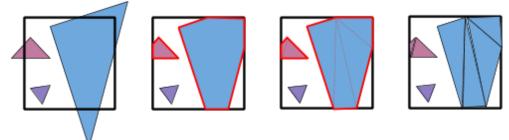

## **Coalesced Global Memory Access**

It's much more efficient for all threads in a block to access global memory locations that are close together.

This basically has to do with memory caching. When a thread fetches (or stores) data in global memory, the GPU accesses that memory in large chunks. If other threads also try to fetch global memory data that's near the same location, those fetches will likely fall into that same large chunk. As such, the GPU won't need to pull down that same large chunk because it'll already be there.

Typical access pattern...

• contiguous  $\leftarrow$  this is good because mem being accessed is neighbouring each other

strided ← this is bad (if too large) because a bunch of mem is skipped for each access

• random  $\leftarrow$  this is bad because it's just randomly grabbing data

**NOTE**: You can optimize the strided pattern to be coalesced. Check out Data Layout Transformation section below.

**NOTE**: All of this just means that the GPU is most efficient when the threads read from and write to contiguous memory locations at the same time.

# **Thread Occupancy**

Occupancy refers to the <u>number of threads that are actually running vs the number of threads</u> <u>that could be running</u>. Each SM has properties that may potentially limit the number of threads it can run (e.g. number of cores, amount of memory, number of registers, etc..).

For example, shared memory for a thread block sits on the SM. If the SM has 48kb of shared memory space available and your thread blocks are for 24kb of shared memory each, you're going to be limited to 2 blocks per SM.

Another example is the number of threads per thread block. If the SM has 1568 cores but your thread block requires 1024 threads per SM, each SM will only ever run 1 block. In this case we can say that we have a occupancy rate of 66% -- the SMs will never use more than 1024 of their 1568 threads.

**NOTE**: Look up CUDA occupancy calculator -- it's a spreadsheet/tool that will tell take in the specs of your thread block and return back how that block will perform on various CUDA GPUs.

# **Thread Divergence**

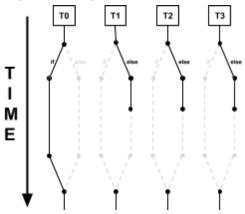

The GPU likes it when all your threads go through the same execution path. <u>If threads end up</u> taking a different execution path, the threads that finish first will end up waiting for the longer executing threads to catch up. This may become a problem if your threads have lots of loops and/or control structures (e.g. if/elseif/else, switch, for, while, do/while, etc..).

**NOTE**: It almost sounds like a block/SM/whatever may give the user a view that multiple threads are executing, but internally it only executes 1 thread -- 1 instruction at a time, but that instruction takes in a ton of different operands (supplied by each "thread"/kernel instance). But, if this were the case, why would we need \_\_synchthreads()?

The answer to this is explained in lesson 5. The SMs in CUDA GPUs are made up of "warp cores." These "warp cores" are an NVIDIA extension to the concept of SIMD (single instruction, multiple datasets) called SIMT (single instruction, multiple threads). It looks like SIMT is essentially the same thing as SIMD. It operates on 32 operands (max of 32 threads per warp core), but you can turn on/off which operands are being worked on.

For example, if you reach a if/else statement, <u>the warp core will execute both branches</u> -it'll first execute the if block (only affecting the data for the threads that should be taking the if branch), then execute the else (only affecting the data for the threads that should be taking the if branch).

For example, imagine if you had the following if/else block in your kernel...

```

// ... code before ...

if (threadIdx.x == 0) {

// takes a long time to finish

} else {

// takes a short time to finish

}

// ... code after ...

```

The block above looks like it will take a long time to execute only for thread 0, but this isn't the case. All threads will wait until thread 0 finishes before they continue executing. It doesn't matter

that the vast majority of your threads finish the if/else quickly -- they will all pause until the longest running thread finishes.

For example, imagine if you have had the following loop block in your kernel...

```

// ... code before ...

for (int i = 0; i < threadIdx.x * 1000; i++) {

val = val * val;

}

// ... code after ...</pre>

```

The same thing applies for loops. The block above looks like it'll take progressively longer to execute as the threadIdx goes up, but that isn't the case. Threads that finish executing the loop will just pause until the longest running thread is finishes executing the loop.

The take away here is to avoid large switches, nested if/elses, and looping by non-constants.

# Thread Synchronization and Memory Access

One important fact about thread blocks is that <u>it isn't always a good thing to have more threads</u> <u>per block</u>. In certain cases, having lots of threads in a thread block where \_\_\_syncthreads() calls are used will cause those threads to run slower. This is because many of the threads will be waiting on memory access operations to complete.

This is more likely to happen if the code has poor memory access patterns (e.g. large strides or scattered/random access).

# Fast Math

Certain common operations from the C/C++ math library (math.h) may take a long time to execute on a GPU. CUDA provides optimized math functions via built-ins/intrinsics. For example, instead of...

- sin(), use \_\_sin()

- cos(), use \_\_cos()

- exp(), use\_exp()

The downside to these built-in/intrinsics math functions is that you may lose a few bits of precision (which should be okay most of the time). You can find more on intrinsics by going to <a href="http://docs.nvidia.com/cuda/cuda-math-api/index.html">http://docs.nvidia.com/cuda/cuda-math-api/index.html</a>.

In addition to that, you can get better execution times by using single-precision floating point vs double-precision floating point. Avoid double-precision unless you absolutely need it (this is common knowledge).

# Memory Copy (Host 5 Device)

CUDA reserves a page-locked (pinned) piece of memory on the host as a staging area for transferring data to the GPU. When you copy data from the host to the GPU, what's actually happening is that memory is first being copied over to that staging area, then being sent from that staging area to the GPU.

You can avoid the staging area entirely by page-locking the part of host memory that you're working with. If you...

- already have host memory allocated, you can page-lock it via <u>cudaHostRegister()</u>.

- want to allocate host memory that's page-locked, you can use <u>cudaHostMalloc()</u>.

In addition to skipping the staging area, if you page-locked your host memory you can make use of <u>cudaMemCpyAsync()</u> to transfer the memory asynchronously -- it won't be a blocking operation, you can do other stuff while the memory transfer completes.

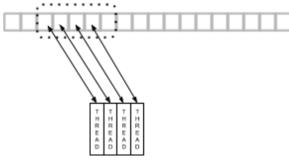

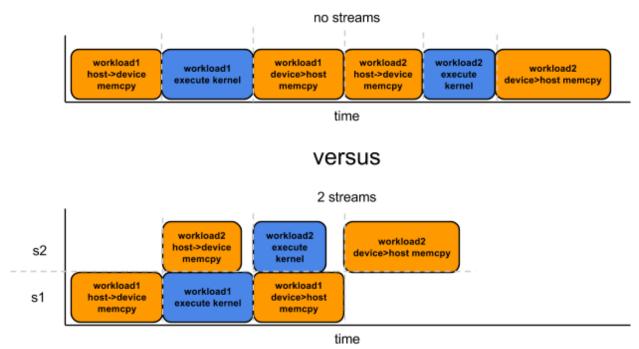

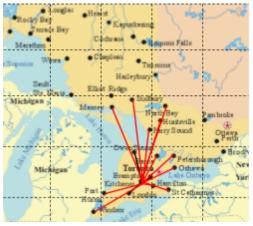

### Streams

A stream is a sequence of CUDA operations that will execute in-order. You can have multiple streams in your program... the benefit being that the <u>operations in each stream will execute as</u> <u>GPU capacity becomes available, potentially executing more than one operation at once</u> (higher utilization).

For example, imagine you had 2 workloads. Each workload copies some data to the GPU, runs a kernel, and then copies data back. If this was implemented normally, the operations would

execute serially. If implemented using streams, the GPU takes care of when each operation is performed, potentially even running multiple operations at once...

In the above diagram, the GPU is copying over data for the 2nd workload while the kernel for the 1st workload is running, then copying over the results of the 1st workload while the kernel for the runs. These are the types of optimizations you can expect from using streams...

- not enough memory bandwidth utilized? copy data over for another stream.

- not enough SMs in use? run another stream's kernel.

- etc...

**NOTE**: The diagram above is a common way of getting better GPU utilization when you need to do computations on a huge amount of data (so big it won't fit into GPU memory). Instead of allocating all of the GPU's memory and running the kernel, allocate it in halves then run the same kernel in 2 separate streams. While the 1st stream is running the 2nd stream will be moving data (and vice versa). You can try maybe doing this with more than 2 streams as well?

Some things to note about using streams...

- 1. if using streams, operations get queued up and run asynchronously.

- 2. if using streams, you must pin host memory (see memory copy section above).

- 3. if using streams, <u>you must use cudaMemCpyAsync</u> (see memory copy section above).

Check out <u>http://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html#streams</u> for more information on streams. Below is a small example that show how to use stream with the CUDA C++ compiler.

```

cudaStream_t stream1, stream2, stream3, stream4 ;

cudaStreamCreate ( &stream1) ;

// ...

cudaMalloc ( &dev1, size ) ;

cudaMallocHost ( &host1, size ) ; // pinned memory required on host

// ...

cudaMemcpyAsync ( dev1, host1, size, H2D, stream1 ) ;

kernel2 <<< grid, block, 0, stream2 >>> ( ..., dev2, ... ) ;

kernel3 <<< grid, block, 0, stream3 >>> ( ..., dev3, ... ) ;

cudaMemcpyAsync ( host4, dev4, size, D2H, stream4 ) ;

some_CPU_method ();

```

**NOTE**: Need to block until all your streams are done? Check out <u>cudaDeviceSynchronize()</u>. Need to block until a single stream is done? Check out <u>cudaStreamSynchronize()</u>. There are also APIs available for waiting on / firing off event: <u>cudaEventRecord()</u>, <u>cudaEventSynchronize()</u>, <u>cudaStreamWaitEvent()</u>, and <u>cudaEventQuery()</u>. You can use these event APIs directly within the kernel if you want -look up dynamic parallelism.

# Algorithm Complexity

# Work Complexity vs Step Complexity

Parallel algorithms on the GPU are calculated as step complexity and work complexity...

- step complexity  $\rightarrow$  complexity of algorithm if run parallelly

- work complexity  $\rightarrow$  complexity of algorithm if run serially/sequentially

Imagine the following chain of work...

We can say the example has a step complexity of 3 and a work complexity of 8. Each level/depth is a step, but each node is a piece of work. Work nodes at each step are generating some output, and the work nodes in the following steps are that output for their input.

In the real world, this is effectively just like big O notation. Instead of saying that the work/step complexity is some specific number, we refer to as a function of the size of the input. For example...

- the work efficiency is proportional to sizeof(input) / O(n)

- the work efficiency is proportional to sizeof(input)<sup>2</sup> / O(n<sup>2</sup>)

- the step efficiency is proportional to log(sizeof(input)) / O(log(n)

- etc..

# Work Efficiency

We can say our parallel algorithm is <u>work efficient</u> if it's asymptotically the same -- within a constant factor as the work complexity of its non-parallel equivalent.

<u>All this means is that your parallel algorithm's complexity isn't more than the complexity of the</u> <u>serial equivalent</u>: if in the serial version you're looping over your array once for each element, in the parallel version you don't want to be looping over the entire array once for each element: O(n) vs  $O(n^2)$ . This is assuming you're doing more-or-less the same thing in the loop.

You can get a good better idea of work efficency means by reading this page <u>https://developer.nvidia.com/gpugems/GPUGems3/gpugems3\_ch39.html</u> (sections 39.1 and 39.1.1). I've pasted the important most important part below...

A simple and common parallel algorithm building block is the all-prefix-sums operation. In this chapter, we define and illustrate the operation, and we discuss in detail its efficient implementation using NVIDIA CUDA. Blelloch (1990) describes all-prefix-sums as a good example of a computation that seems inherently sequential, but for which there is an efficient parallel algorithm. He defines the all-prefix-sums operation as follows:

The all-prefix-sums operation takes a binary associative operator  $\oplus$  with identity I, and an array of n elements

$[a_0, a_1, ..., a_{n-1}]$ and returns the array  $[I, a_0, (a_0 \oplus a_1), ..., (a_0 \oplus a_1 \oplus ... \oplus a_{n-2})]$

For example, if  $\oplus$  is addition, then the all-prefix-sums operation on the array [3 1 7 0 4 1 6 3] would return [0 3 4 11 11 15 16 22].

The all-prefix-sums operation on an array of data is commonly known as *scan*. We use this simpler terminology (which comes from the APL programming language [Iverson 1962]) for the remainder of this chapter. The scan just defined is an *exclusive* scan, because each element *j* of the result is the sum of all elements up to but *not including j* in the input array. In an *inclusive* scan, all elements *including j* are summed. An exclusive scan can be generated from an inclusive scan by shifting the resulting array right by one element and inserting the identity. Likewise, an

inclusive scan can be generated from an exclusive scan by shifting the resulting array left and inserting at the end the sum of the last element of the scan and the last element of the input array (Blelloch 1990). For the remainder of this chapter, we focus on the implementation of exclusive scan and refer to it simply as "scan" unless otherwise specified.

There are many uses for scan, including, but not limited to, sorting, lexical analysis, string comparison, polynomial evaluation, stream compaction, and building histograms and data structures (graphs, trees, and so on) in parallel. For example applications, we refer the reader to the survey by Blelloch (1990). In this chapter, we cover summed-area tables (used for variable-width image filtering), stream compaction, and radix sort.

In general, all-prefix-sums can be used to convert certain sequential computations into equivalent, but parallel, computations...

```

// sequential version

out[0] = 0;

for j from 1 to n do

out[j] = out[j-1] + f(in[j-1]);

// parallel version

forall j in parallel do

temp[j] = f(in[j]);

all_prefix_sums(out, temp);

```

Implementing a sequential version of scan (that could be run in a single thread on a CPU, for example) is trivial. We simply loop over all the elements in the input array and add the value of the previous element of the input array to the sum computed for the previous element of the output array, and write the sum to the current element of the output array.

out[0] := 0 for k := 1 to n do out[k] := in[k-1] + out[k-1]

This code performs exactly *n* adds for an array of length *n*; this is the minimum number of adds required to produce the scanned array. When we develop our parallel version of scan, we would like it to be *work-efficient*. A parallel computation is work-efficient if it does asymptotically no more work (add operations, in this case) than the sequential version. In other words the two implementations should have the same *work complexity*, O(n).

# **Algorithm Primitives**

The following subsections define a common set of primitives for highly parallel algorithms.

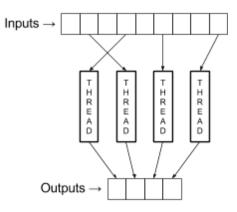

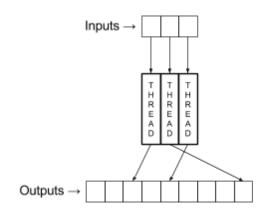

# Мар

A map operation takes each data element (e.g. elements of an array, entries in a matrix, pixels in an image, etc...) and performs the same computational task on that element to produce a result. There's a one-to-one correspondence between input and output.

Potential use-cases...

- 1. transforming a number via some equation

- 2. turning an image to grayscale

- 3. blurring an image

- 4. transposing an 2d matrix

- 5. breaking up a struct  $\rightarrow$  array of structures (AOS) to a structure of arrays (SOA)

#### **Special Cases**

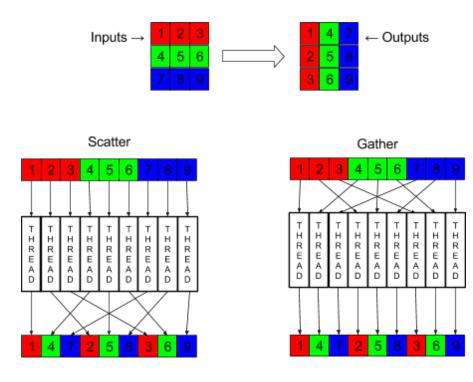

#### Gather

A gather operation is a map, but there's only a one-to-one relationship <u>from output to input</u>. Every output location has a corresponding input location, but not every input location has a corresponding output location.

**NOTE**: See the section on "Coalesced Global Memory Access" to see why this can be a bad pattern.

#### Scatter

A gather operation is a map, but there's only a one-to-one relationship <u>from input to output</u>. Every input location has a corresponding output location, but not every output location has a corresponding input location.

**NOTE**: The output location isn't guaranteed to be unique. If there's a possibility for multiple threads to write to the same location (remember that all threads run at the same time), you're going to run into problems. It hasn't been clearly explained how to handle this yet.

**NOTE**: See the section on "Coalesced Global Memory Access" to see why this can be a bad pattern if not implemented correctly.

**NOTE**: One of the use-cases described for this was applying an image. How exactly can this be used to blur an image? We can take the input pixel and add a 1/3rd of it to each output.

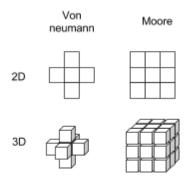

#### Stencil

A stencil operation is where the thread reads input from a <u>fixed neighbourhood within in array</u> and produces some output. This is useful for things like image processing.

Common shapes for stencils include...

#### Transpose

A transpose operation is a plain old transpose operation such as ones you would do with a matrix. It can be considered a special case of either gather or scatter.

Transpose operations can also be used for reordering or breaking up a structure -- converting an array of structures (AOS) to a structure of arrays (SOA). Imagine the following struct...

```

struct my_struct {

float f;

int i;

}

```

We can convert my\_struct[1000] to float[1000] + int[1000]. It's useful to break up structs like this if we're doing heavy computations that mostly access certain bits (e.g. the floats). This is called the principle of locality.

**NOTE**: We can also consider reordering the members of a struct as a transpose operation (reordering vs purely breaking them apart).

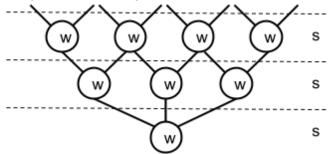

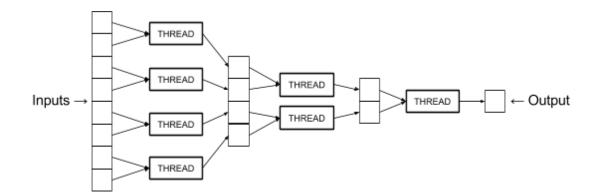

### Reduce

A reduce operation is where threads aggregate a bunch of data together. This is done in multiple steps and leads to a single output.

The operator you use in your reduce must follow these rules...

<u>binary</u> ← takes in 2 inputs

The binary property essentially halves the data at each step. The operator takes in 2 inputs but gets back 1 output, so you can keep running it iteratively until you end up with your final output.

<u>associative</u> ← order in which operator is applied doesn't matter Associative means you can choose to do your operations in any order. For example, if your operator was addition and your inputs were a, b, and c, you could add them in any order and get to the same result. If a=1, b=2, c=3... (1+2)+3=6 1+(2+3)=6

Why is this needed? It guarantees that the same result is given back regardless of the order in which threads run.

**NOTE**: We make the assumption that associativity implies commutativity. Commutativity means that the operands going in can be in any order. For example, a+b=b+a.

Some ops that pass the requirements...

- addition (+)

- multiplication (\*)

- bitwise and

- bitwise or

- min/max

Some ops that fail the requirements:

- subtraction (-) ← not associative... (a-b)-c != a-(b-c)

- division (/) ← not associative... (a/b)/c != a/(b/c)

- exponent ← not associative... pow(pow(a,b),c) != pow(a,pow(b,c))

- factorial (!) ← factorial takes 1 input, not 2... e.g. 5!

Potential use-cases...

- 1. finding min or max of a large set of numbers

- 2. adding a bunch of numbers together

#### Implementations

Serial

Below is a CPU implementation of reduce. The implementation is using addition (+) as its operator...

#### Output is...

27

Parallel

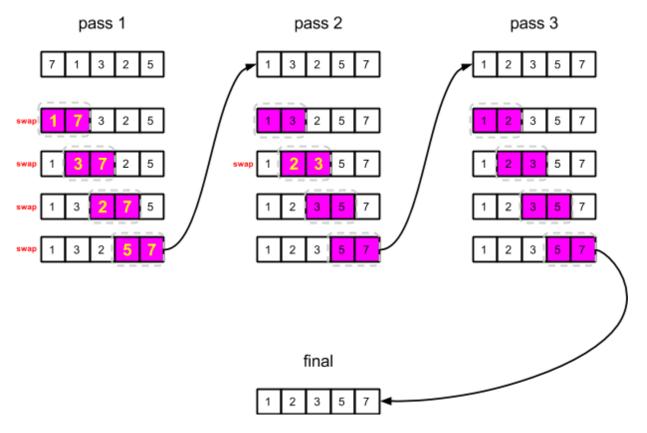

**NOTE**: Remember the difference between work and step. Work refers to a unit of work. Step refers to multiple units of work being done in parallel.

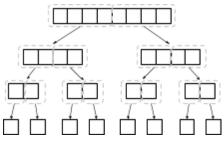

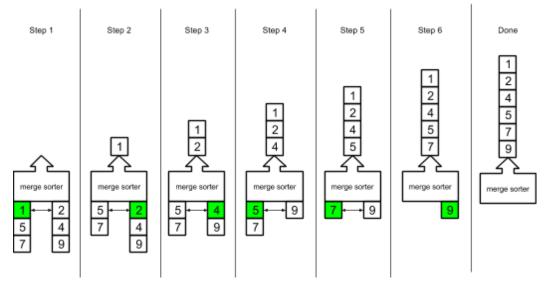

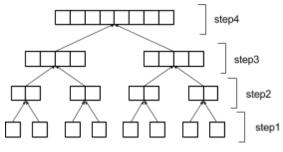

For example, imagine you wanted to reduce 8 numbers via the addition operator. Conceptually, here's how the entire process would look...

Notice what's happening here. There are 3 steps. The work in each step is being done in parallel...

1. 4 threads will run in parallel, each will perform one of the following ops:

1+4=5

- 2+2=4

- 1+0=1

- 4+1=5

- 2 threads will run in parallel, each will perform one of the following ops: 5+4=9 1+5=6

- 1 thread will run, it will perform the following op: 9+6=15

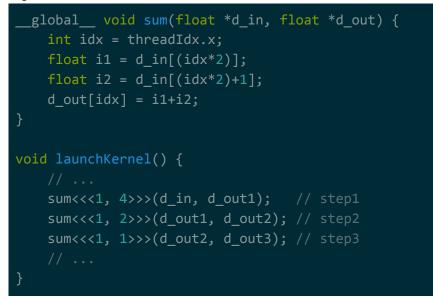

If you were to code this example up, it would just be 3 launches of a kernel that adds 2 numbers together...

Essentially, this means we can reduce a large amount of inputs in a small number of steps. In our example, we summed up 8 elements in 3 steps. If we wanted to sum up 65536 elements instead, that would come out to 16 steps.

The work complexity of reduce is around O(n-1). The step complexity of reduce is around  $O(\log_2(n))$ .

**NOTE**: Having trouble reasoning out the complexity for this? Imagine we had 8 inputs and we were reducing it using the + operator...

8 inputs (this is n)

7 work operations (this is n-1)

3 step operations (this is log<sub>2</sub>(n))

**NOTE**: As an optimization, you can always cluster together multiple runs of the operator in your thread. For example, instead of just adding 2 inputs together, you can just to add 10 or 20 inputs.

## **Practical Considerations**

#### Number of Parallel Units

What happens if we try to reduce a massive amount of elements (e.g. a billion elements)? At each step, our GPU can only run so many threads in parallel. If we go past this cap, the GPU may internally break steps into multiple pieces that it runs sequentially. Look up "Brent's theorem" for a deeper dive into this topic.

## Floating Point Arithmetic / Non-associative Operators

What happens if you choose an operator that isn't associative? It may still be okay to use this pattern. For example, think of floating point numbers. Arithmetic on floating point numbers is not associative. <u>This doesn't mean you can't use reduce</u>, it just means that you may not get consistent results between runs for the same inputs. This is due to the fact there is no guarantee that threads will execute in the same order. You may be processing in a different order each time.

**NOTE**: If you're having trouble thinking of how floating point arithmetic is not associative, try (a+b)+c != a+(b+c) - plug into any c compiler where a=1,  $b=10^{10}$ ,  $c=-10^{10}$ .

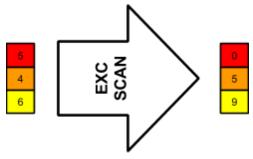

# Scan

A scan operation is that transforms an array of elements such that each element becomes the aggregate of all elements preceding it.

**NOTE**: There is no thread representation diagram here because this is a combination of other patterns and there are several implementations of it.

The operator you use for aggregation in your scan must follow these rules...

- <u>binary</u> ← takes in 2 inputs

- <u>associative</u> ← order in which operator is applied doesn't matter

- identity ← must have some constant value I where f(I,b)=b

This rules are similar to the rules for reduce, but with the additional restriction of needing to have an identity constant. If you need more information on what binary and associativity do, see the reduce section. If you're wondering about identity, here are the identity values of common operators...

- addition (+)  $\rightarrow$  0 e.g. 5+0=5

- multiplication (\*)  $\rightarrow$  1 e.g. 5\*1=5

- binary or  $\rightarrow 0$  e.g. or(1,0)=1 or(0,0)=0

- binary and  $\rightarrow 1$  e.g. and(0,1)=0 and(1,1)=1

- max  $\rightarrow$  MIN\_INT e.g. max(MIN\_INT, 10)=10

- min  $\rightarrow$  MAX\_INT e.g. min(MAX\_INT, 10)=10

**NOTE**: MIN\_INT/MAX\_INT are defined by the type you're working with. For example, if you're working with an unsigned char, MIN\_INT=0 and MAX\_INT=0xFF.

Having trouble understanding this? Imagine that we wanted to do a scan of the array [1, 2, 3, 4] using + as the operator. Here's how we calculate each element of the output array... [0, 1, 1+2, 1+2+3]  $\rightarrow$  [0, 1, 3, 6]

For each element, we're aggregating (adding in this case) all the elements preceding it. The first element has nothing preceding it so it's set to the identity.

Potential use-cases...

- 1. cumulative distribution function

- 2. quicksort

- 3. etc..

## Variations

There are actually 2 forms of scan: inclusive and exclusive...

- Inclusive: each element will be the aggregate of all elements <u>before and including</u> it.

[a₀, a₁,..., aₙ₋₁] → [a₀, (a₀?a₁),...,(a₀?a₁?...?aₙ₋₁)]

- Exclusive: each element will be the aggregate of all elements <u>before</u> it.

[a<sub>0</sub>, a<sub>1</sub>,..., a<sub>n-1</sub>] → [I, a<sub>0</sub>, (a<sub>0</sub>?a<sub>1</sub>),...,(a<sub>0</sub>?a<sub>1</sub>?...?a<sub>n-2</sub>)]

Replace <u>?</u> with the operator of your choice (e.g. +, \*, etc..) and <u>I</u> with the identity for that operator. Remember that the operator must have an identity, must be binary, and must be associative+commutative.

**NOTE**: If you wanted to be super explicit, you can write exclusive as...

$[a_0, a_1, ..., a_{n-1}] \rightarrow [I, (I?a_0), (I?a_0?a_1), ..., (I?a_0?a_1?...?a_{n-2})]$

If you have trouble thinking about this, try use the operator + (identity is 0) or \* (identity is 1). It should work.

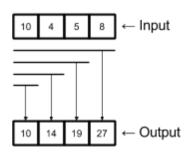

For example, imagine you had the array [10, 4, 5, 8] and you wanted to scan over it using + as the operator...

• Inclusive:  $[10, (10+4), (10+4+5), (10+4+5), (10+4+5+8)] \rightarrow [10, 14, 19, 27]$ • Exclusive:  $[0, 10, (10+4), (10+4+5), (10+4+5)] \rightarrow [0, 10, 14, 19]$  **NOTE**: Remember that the form for exclusive puts the identity for addition as the first element and doesn't take into account the last element. Remember that the identity for addition is 0: x+0=x.

What's the point of having 2 different variations of a scan? As far as I know, there are 2 different algorithms for performing a scan in parallel (discussed in later section). One of the algorithms produces an exclusive result, while the other algorithm produces an inclusive result.

It seems fairly trivial to convert one type of result to the other 2...

- $I \rightarrow E$ : shift right by 1 then add a 0 to the last element

- $E \rightarrow I$ : shift left by 1 then do a reduce over the original array to get last element

**NOTE**: Remember that shifting a large array left/right by 1 is a super fast thing to do in parallel computing.

## Implementations

## Serial

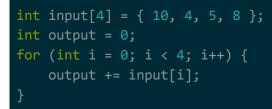

Below is a CPU implementation of an inclusive scan. The implementation is using addition (+) as its operator...

```

int input[4] = { 10, 4, 5, 8 };

int output[4];

int acc = 0; // set this to the identity.. 0 for addition

for (int i = 0; i < 4; i++) {

// flip these 2 lines to switch to exclusive scan

acc += input[i];

output[i] = acc;

}

```

## Output is...

10 14 19 27

## Parallel (Naive)

A naive parallel implementation for scan would be to use reduce for each element on the input array, where the reduce targets everything up to and including that element.

For example, imagine you were to perform an inclusive scan on the array [10, 4, 5, 8] using + as the operator...

- Index 0: reduce([10], +)

- Index 1: reduce([10,4], +)

- Index 2: reduce([10,4,5], +)

• Index 3: reduce([10,4,5,8], +)

Note that you can perform multiple reduces in parallel. Practically speaking, you start from index 0 of the input array and work your way up until you reach a cap for how many reduces/threads you can run. Then, you'll then have to wait for those reduces to finish before you can move on to the next group of elements. For the next group of elements from the input array, you can make use of the last element you computed in the previous group.

**NOTE**: Having trouble visualizing this? Imagine that the 3rd element in the example was the last element we were able to do a reduce for before you ran out of GPU resources. For the next set of elements, you can directly make use of the result of that 3rd element...

reduce([19, 8], +) vs reduce([10,4,5,8], +)

The work complexity of scan is around  $O(n^2)$ . The step complexity of scan is around O(log(n))

**NOTE**: Remember the difference between work and step. Work refers to a unit of work. Step refers to multiple units of work being done in parallel.

The step complexity for scan is the same as the step complexity for reduce because technically we're just running a whole bunch of reductions at once. The work complexity for scan is  $n^2$  because we go over the elements of the input array once per reduce (we don't go over all elements per reduce, but we can just generalize this as  $n^2$ ).

The n<sup>2</sup> work complexity makes this algorithm "ridiculously inefficient." As such, you should use one of the other less-trivial parallel algorithms discussed in later sections.

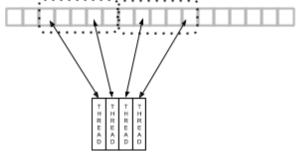

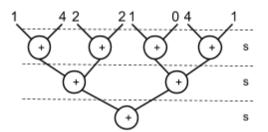

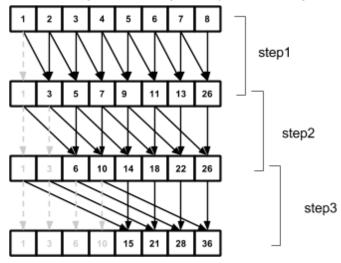

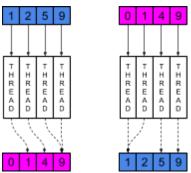

#### Parallel (Hillis-Steele)

Hillis-Steele is a parallel implementation of inclusive scan.

The high-level steps for Hillis-Steele scan algorithm are... at each parallel step

- 1. copy the first 2<sup>step</sup> elements from the input array

- 2. add each remaining element with the element that's 2step to its left

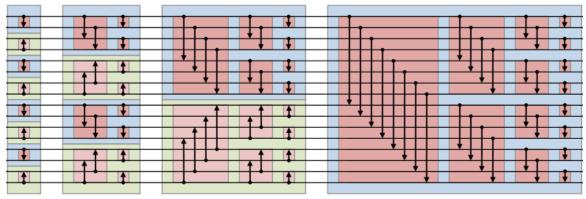

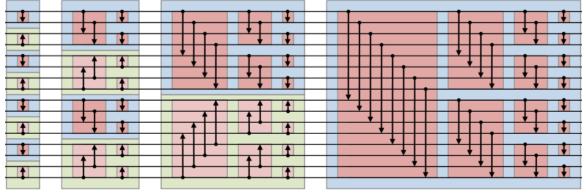

Here's a diagram showing exactly what the algorithm does for the input array [1,2,3,4,5,6,7,8]...

Note that this is much more efficient than the naive parallel implementation of scan. In the case of our example above, there are 8 elements for our scan. Using this implementation, we're doing 3 reduce-like operations. If we used our naive parallel implementation, we'd be doing 8 reduce operations.

Below is a Java implementation of the algorithm written in non-parallel form. The example takes in the array [1,2,3,4,5,6,7,8] and performs a scan on it using addition (+) as the operator...

```

int[] input = {1, 2, 3, 4, 5, 6, 7, 8};

int[] output;

int n = 1;

while (n < input.length) {

// create new output array for this step

output = new int[8];

// copy the first n elements of input to output

for (int idx = 0; idx < n; idx++) {

output[idx] = input[idx];

}

// for each remaining element in input, output[i]=input[i]+input[i-n]

for (int idx = n; idx < input.length; idx++) {

int val1 = input[idx];

int val2 = input[idx - n];

output[idx] = val1 + val2;

}

```

```

System.out.println(Arrays.toString(output)); // print step's output

input = output;

n *= 2;

```

Output of the code is ...

[1, 3, 5, 7, 9, 11, 13, 15] [1, 3, 6, 10, 14, 18, 22, 26] [1, 3, 6, 10, 15, 21, 28, 36]

The last line of the output is the correct result. Although the code above is non-parallel, it should be obvious what parts you can run in parallel: <u>pretty much every iteration of the while loop can</u> <u>be run as a single parallel step</u>.

**NOTE**: Although this is an inclusive scan, it's trivial to convert it to an exclusive scan: shift the final output right by 1 and put the identity value at index 0.

The step complexity is O(log(n)) The work complexity is O(n\*log(n))

**NOTE**: Remember the difference between work and step. Work refers to a unit of work. Step refers to multiple units of work being done in parallel.

If you're having trouble visualizing this, just look at our example. We had an input size of 8 but the number of parallel steps were 3. Try it with smaller or larger step sizes, you should see a pattern like this...

- input size of 2 = 1 parallel step

- input size of 4 = 2 parallel steps

- input size of 8 = 3 parallel steps

- input size of 16 = 4 parallel steps

- etc...

You can see how the number of steps here will  $\log_2(n)$  where n is the size of the input. We generalize this a  $\log(n)$  when we specify the step complexity.

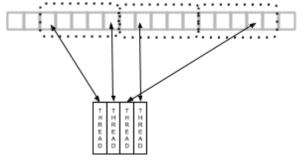

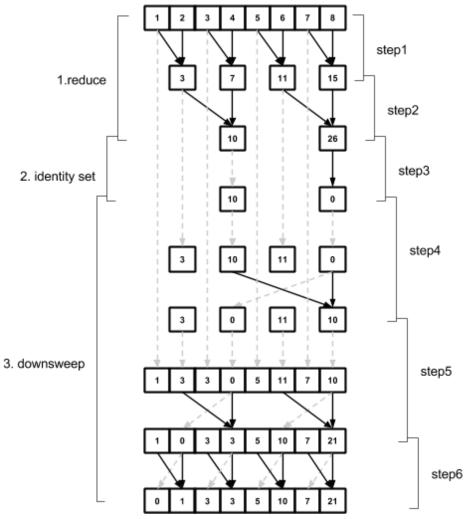

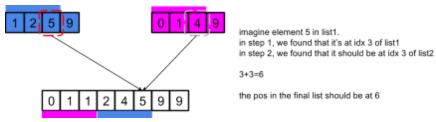

#### Parallel (Blelloch)

Blelloch is a parallel implementation of exclusive scan.

The high-level steps for Blelloch scan algorithm are...

- 1. perform reduce on the input array up to the point where there are only have 2 elements, saving the intermediate results at each step of the reduce

- 2. set the last element of the last step of the reduce to the identity

- 3. down-sweep the array back out to the original input size

- 4. perform one final down-sweep on the array without expanding it

**NOTE**: Remember that the scan operator you use must have an identity value associated with it. If you don't remember what this is, read the main section of the scan section.

What is a down-sweep and how does it work? You can think of the initial reduce as an up-sweep. When we expand it back out to calculate the scan, we call that the down-sweep.

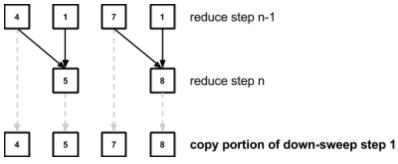

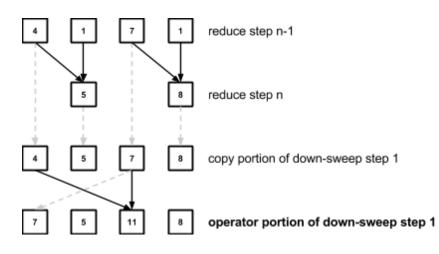

Remember that we saved all the intermediate values of our reduce. So when we perform a down-sweep step, we begin by doubling the size of the array and copying over the missing elements from the previous reduce step. For example....

**NOTE**: Why do we have 2 elements at the end of our reduce? Remember that in step 1 we say that we stop our reduce when we have 2 elements.

Once that's complete, we perform a down-sweep operator on each pair of newly introduced elements. A down-sweep operator copies the right value over to the left, and sets the left value to left OP right. If we were to apply the down-sweep operator to the example above (note that we're using addition as our operator), it would look like this...

Here's a diagram showing exactly what the algorithm does for the input array [1,2,3,4,5,6,7,8] using addition (+) as the operator...

NOTE: Remember that that the identity for addition is 0.

**NOTE**: Look at the last step... we need to apply the down sweep operator to each pair of elements in the final array one last time before we get the result we expect for a scan.

Note that this is much more efficient than the naive parallel implementation of scan. In the case of our example above, there are 8 elements for our scan. Using this implementation, we're effectively just doing 1 reduce operation and 1 downsweep operation. That's around 5 to 6 parallel steps. If we used our naive parallel implementation, we'd be doing 8 reduce operations. In addition to that, we're doing much less work than the naive parallel implementation (the scan operator is applied way less times).

Below is a Java implementation of the algorithm written in non-parallel form. The example takes in the array [1,2,3,4,5,6,7,8] and performs a scan on it using addition (+) as the operator...

```

public static void main(String[] args) {

int[] in = new int[] {1,2,3,4,5,6,7,8};

System.out.println("Reducing...");

int[][] reduce_out = reduce(in);

System.out.println("Resetting final element to 0...");

reduce_out[reduce_out.length-1][1] = 0;

System.out.println(Arrays.toString(reduce_out[reduce_out.length-1]));

System.out.println("Downsweeping...");

downsweep(reduce out);

public static int[][] reduce(int[] input) {

List<int[]> ret = new ArrayList<>();

ret.add(input);

while (input.length > 2) {

int[] output = new int[input.length / 2];

for (int i = 0; i < output.length; i++) {</pre>

output[i] = input[i*2] + input[i*2+1];

ret.add(output);

input = output;

```

```

for (int i = 0; i < ret.size(); i++) {</pre>

System.out.println(Arrays.toString(ret.get(i)));

return ret.toArray(new int[0][]);

public static int[] downsweep(int[][] input) {

int[] last_output = input[input.length - 1];

for (int i = input.length - 2; i >= 0; i--) {

int[] reduce_res_prev = input[i];

int[] output = Arrays.copyOf(

reduce_res_prev,

reduce res prev.length);

for (int j = 0; j < last_output.length; j++) {</pre>

output[(j*2)+1] = last_output[j];

for (int j = 0; j < output.length; j += 4) {</pre>

int val1 = output[j+1];

int val2 = output[j+3];

output[j+1] = val2;

output[j+3] = val1 + val2;

System.out.println(Arrays.toString(output));

last_output = output;

for (int j = 0; j < last_output.length; j += 2) {</pre>

int val1 = last_output[j];

int val2 = last_output[j + 1];

last_output[j] = val2;

last_output[j + 1] = val1 + val2;

```

| Reducing                     |  |  |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|--|--|

| [1, 2, 3, 4, 5, 6, 7, 8]     |  |  |  |  |  |  |  |  |

| [3, 7, 11, 15]               |  |  |  |  |  |  |  |  |

| [10, 26]                     |  |  |  |  |  |  |  |  |

| Resetting final element to 0 |  |  |  |  |  |  |  |  |

| [10, 0]                      |  |  |  |  |  |  |  |  |

| Downsweeping                 |  |  |  |  |  |  |  |  |

| [3, 0, 11, 10]               |  |  |  |  |  |  |  |  |

| [1, 0, 3, 3, 5, 10, 7, 21]   |  |  |  |  |  |  |  |  |

| [0, 1, 3, 6, 10, 15, 21, 28] |  |  |  |  |  |  |  |  |

The last line of the output is the correct result. Although the code above is non-parallel, it should be obvious what parts you can run in parallel.

**NOTE**: Although this is an exclusive scan, it's trivial to convert it to an inclusive scan: shift the final results left by 1 and perform a reduce on the original input to get the value for the last element.

The step complexity is O(log(n)) The work complexity is O(n)

**NOTE**: Remember the difference between work and step. Work refers to a unit of work. Step refers to multiple units of work being done in parallel.

Note that this is the same work and step complexity of a reduce. A downsweep is the opposite of a reduce (we're expanding out rather than reducing), but it's effectively the same amount of work with the same amount of steps. As such, we can say that, for the same amount of data, we're doing 2 reduce operations worth of steps and work. That just gets generalized down to the same work and step complexity as a reduce.

That work and step complexity may seem great, but remember that we have to store the intermediate values of the initial reduce that we do, which means that this is going to be much more memory inefficient.

# **Practical Considerations**

#### Number of Parallel Units and Algorithm Choice

Given the same input array, of the two parallel implementations of scan...

- Hillis-Steele does less parallel steps but more work

- Blelloch does more parallel steps but less work

So which should you choose? It depends on the amount of work you have and the number of parallel units in your GPU. At each step, your GPU can only run so many threads in parallel. If it goes past this cap, the GPU may internally break steps into multiple pieces that it runs sequentially.

If you know that you have more than enough parallel units to handle all the work in each step, use Hillis-Steele. There will be more work being performed per parallel step (more threads per step), but there will be fewer parallel steps and each step will actually run in parallel instead of being broken up.

If you know that you don't have enough parallel units to handle all the work in each step, go for Blelloch. There will be more parallel steps, but much less work will be happening in each parallel step (less threads per step). As such, it'll be far more likely that each step will actually run in parallel instead of being broken up.

Look up "Brent's theorem" for a deeper dive into this topic.

Floating Point Arithmetic / Non-associative Operators

This is from the section on reduce, but it applies to scan as well...

What happens if you choose an operator that isn't associative? It may still be okay to use this pattern. For example, think of floating point numbers. Arithmetic on floating point numbers is not associative. <u>This doesn't mean you can't use scan</u>, it just means that you may not get consistent results between runs for the same inputs. This is due to the fact there is no guarantee that threads will execute in the same order. You may be processing in a different order each time.

**NOTE**: If you're having trouble thinking of how floating point arithmetic is not associative, try (a+b)+c != a+(b+c) - plug into any c compiler where a=1,  $b=10^{10}$ ,  $c=-10^{10}$ .

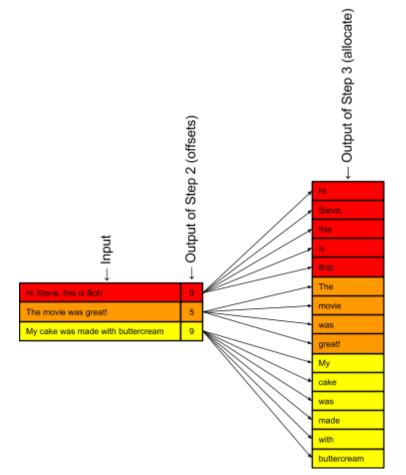

#### Segmented Scan

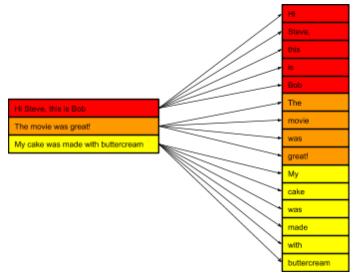

Recall that kernels run one at a time, back-to-back. In a lot of cases you'll be doing scans for many small arrays instead of a few large arrays. In those cases, you can try to implement a technique known as segment scan.

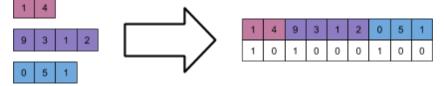

Segmented scan involves concatenating your input arrays together and then having a secondary array that identifies segment heads (where each individual array starts in the concatenated array). The kernel will use this information to scan all the arrays at once...

**NOTE**: The assumption here seems to be that Hillis-Steele and Blelloch can be tweaked to handle this? I still need to work out how to do this.

# Algorithm Patterns

The following subsections discusses how common algorithms can be implemented in parallel.

# Histogram

A histogram is where, for each input, you dump that input into a bucket based on the range that it sits in.

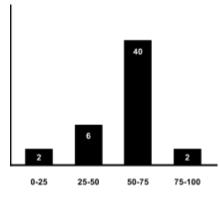

For example, let's say you have the test scores for 50 students. You want to split those scores up into 4 buckets to see how well/poorly the students did overall: 0-25, 25-50, 50-75, 75-100. For each test score, find out what bucket that test score is in and add 1 to it...

Serial

Python example...

```

input_data = [15,11,2,25,4,5,6,7,10,49,1,3,4]

histo = [0, 0, 0, 0, 0]

for e in input_data:

```

```

idx = e // 10

histo[idx] += 1

print(str(histo))

```

[8, 3, 1, 0, 1]

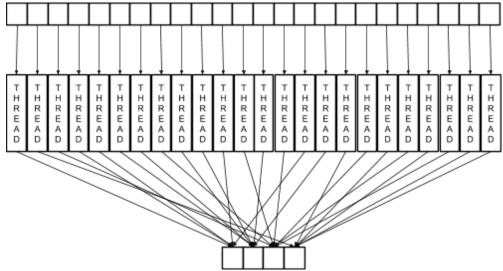

## Parallel (Atomic Add)

Launch a thread for each element and have each thread...

- 1. calculate which bucket the input is in

- 2. perform an atomicAdd on to that bucket

This is a really bad idea if you have a low number of buckets. Because many threads will be trying to add to that same bucket at the same time, threads adding to the same bucket will have to queue up and perform the add sequentially. This kills the whole point of having many parallel threads.

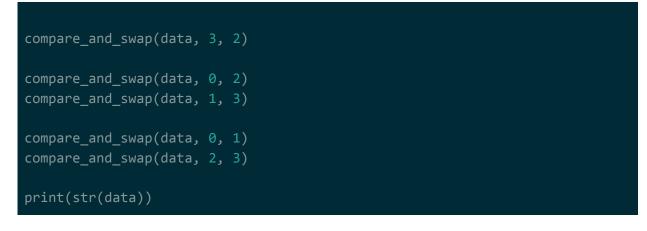

#### Python example...

```

pos = cuda.threadIdx.x + cuda.blockIdx.x * cuda.blockDim.x

val = in_data[pos]

bucket = val // 10

cuda.atomic.add(out_data, bucket, 1)

in_data = np.random.randint(0, 50, 10000)

out_data = np.zeros(5, dtype=np.int32)

hist[10, 1000](in_data, out_data)

print(str(out_data))

```

[2036 1993 1928 2001 2042]

# Parallel (Thread Local Histogram and Atomic Add)

Launch a thread for each n elements and have each thread...

- 1. calculate the histogram locally just for those n elements (sequentially)

- 2. for each bucket in the local histogram, atomicAdd it to the corresponding global histogram bucket

For a low bucket size, this is better than the first parallel method because there won't be as much contention (there are much less atomicAdds happening). On the down side, we're potentially losing some parallelism because each thread is doing a bunch of work sequentially. Depending on how you set things up (number of parallel threads the GPU can run, cost of

booting up a new thread, how much the contention from atomicAdd costs, etc..), this may not be a problem.

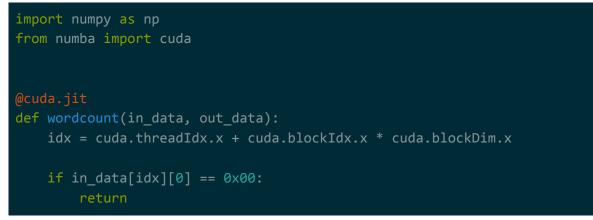

Python example...

```

import numpy as np

from numba import cuda, int32

BUCKETS = 5

MAX VAL = 50

RANGE = MAX_VAL / BUCKETS

ELEM PER THREAD = 100

def hist(in data, out data):

idx = cuda.threadIdx.x + cuda.blockIdx.x * cuda.blockDim.x

# create local histogram array

out local = cuda.local.array(BUCKETS, int32)

for i in range(0, BUCKETS):

out local[i] = 0

for i in range(0, ELEM_PER_THREAD):

val = in_data[idx][i]

bucket = int(val / RANGE)

out_local[bucket] += 1

for i in range(0, BUCKETS):

val = out local[i]

cuda.atomic.add(out_data, i, val)

np.random.seed(0)

in_data = np.random.randint(0, MAX_VAL, [65536, ELEM_PER_THREAD])

out_data = np.zeros(BUCKETS, dtype=np.int32)

hist[8, 1024](in_data, out_data)

```

# print(str(out\_data))

#### Output is...

#### [163866 163560 163849 163700 164225]

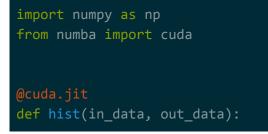

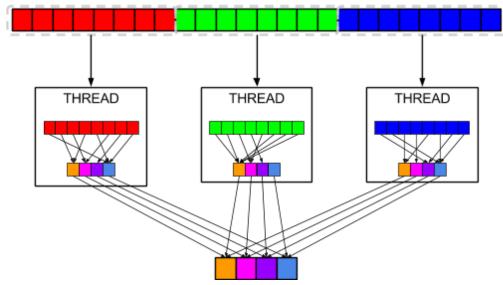

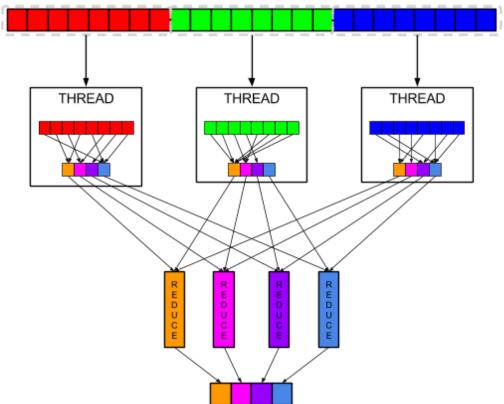

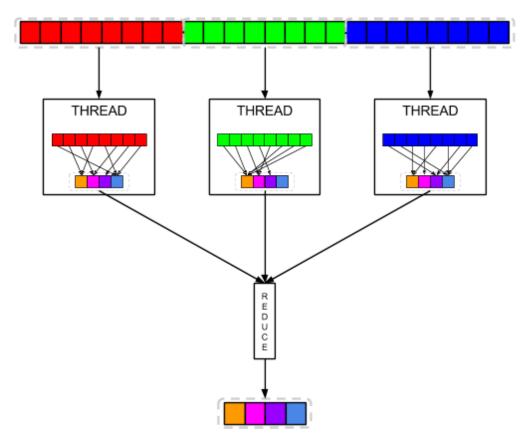

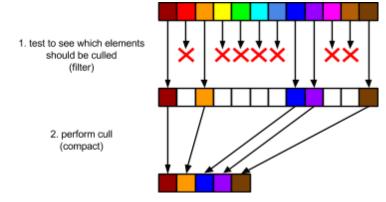

# Parallel (Thread Local Histogram and Reduce)

Launch a thread for each n elements and have each thread calculate the histogram locally just for those n elements (sequentially). Then, once all the local histograms have been computed, you run them through a reduce (addition) to get the global histogram.

The trivial way to do reduce would be, for each index i, run a reduce for that element across all local histograms and put it in the corresponding index for the global histogram...

A less-trivial way to do reduce would be to treat each local histogram as a vector/matrix, and use vector/matrix addition as your reduce operator. Essentially, we're going to be doing a single reduce because we'll be treating each local histogram as an input element for the reduce. This will spawn less threads but it'll do more work per thread -- whether this is better or worse depends on your setup.

**NOTE**: Remember that reduce requires an operator that takes 2 inputs (binary) and is associative/commutative. The vector/matrix addition meets both criteria.

#### Python example...

```

import numpy as np

from numba import cuda

BUCKETS = 5

MAX_VAL = 50

RANGE = MAX_VAL / BUCKETS

ELEM_PER_THREAD = 100

@cuda.jit

def hist_local(in_data, out_data):

idx = cuda.threadIdx.x + cuda.blockIdx.x * cuda.blockDim.x

# compute local histogram

```

```